# 2차원 부호화 기법을 이용한 7.43Gb/s (70528, 65536) 연접-BCH 부호화기

\*이영주, 유호영, 정재환, 조지혁, 박인철 한국과학기술원 전기 및 전자공학과 e-mail: yjlee.ics@gmail.com

A 7.43Gb/s (70528, 65536) Concatenated-BCH Encoder Using Two-dimensional Encoding Scheme

\*Youngjoo Lee, Hoyoung Yoo, Jaehwan Jung, Jihyuck Jo, In-Cheol Park

Department of Electrical Engineering

Korea Advanced Institute of Science and Technology

#### Abstract

In this paper, we present a 32-parallel, 7.43Gb/s concatenated-BCH (CBCH) encoder architecture for solid-state drives (SSDs). A novel two-dimensional encoding scheme is proposed to process row-wise and column-wise computations at the same time. As the encoding of a CBCH codeword is done by using the user-date only once, the encoding throughput is improved twice without increasing the parallelism. The proposed 8KB CBCH encoder is implemented in 65nm CMOS process, and achieves an encoding throughput of 7.43Gb/s at the speed of 250MHz.

## I. 서론

NAND 플래시 메모리는 보다 향상된 공정과 하나의 셀에 여러 비트를 저장하는 multi-level cell (MLC) 기법의 확장을 통하여 점진적으로 비트-코스트를 줄여가고 있다[1]. 이로 바탕으로 최근에는 다수의 MLC NAND 플래시를 기반으로 하는 solid-state drive (SSD)가 스토리지 시장을 빠르게 점유하고 있다. 하지만 MLC NAND 플래시는 메모리셀 내부의 정보량간

의 물리적 거리가 가까워짐에 따라 기존의 저장장치에 비하여 매우 높은 오류율을 갖는 단점이 존재한다. NAND 플래시 기반의 SSD에서는 이를 해결하기 위한 강력한 오류정정부호의 활용이 필수적이다. NAND 플래시에서 soft-정보를 얻는 과정은 복잡하기에 hard-정보만을 이용하면서도 낮은 page-error rate (PER)을 실현하는 것이 필요하다[2-3]. 이를 위하여 최근에 보고된 8KB 연접-BCH (CBCH) 부호는 hard-정보만을 이용하면서도 높은 오류정정능력을 보여 차세대 SSD시스템에 적합하다[4]. 하지만 기존의 CBCH 부호화기는 row-방향의 부호화를 마친 후에 column-방향의 부호화를 시작하는 1차원 부호화를 사용하여 고속의 인터페스와 연결되는 SSD를 지원할 수 없다[5].

본 논문에서는 S-ATA III, PCIe 등의 최신 고속 인터페스에서 요구되는 6Gb/s급 이상의 부호화 속도를 만족하는 CBCH 부호화기를 기술한다. 제안된 2차원부호화 기법은 row-방향의 부호화가 진행되는 동안에 column-방향의 부호화를 부분적으로 수행하여, 8K-바이트의 사용자-데이터를 한 번만 사용하면서도 row-방향 부호와 column-방향 부호를 동시에 계산한다. 따라서 제안된 부호화 기법은 기존에 1차원 부호화 방식에 비하여 부호화 속도를 2배 향상시킨다. 제안된 2차원 부호화 과정을 이용한 32-parallel CBCH 부호화기는 65nm CMOS 공정에서 구현되었으며, 250MHz의동작속도에서 7.43Gb/s의 부호화 속도를 실현하였다.

#### 2013년도 대한전자공학회 하계학술대회 제36권 1호

# II. 본론

#### 2.1 (70528, 65536) CBCH 부호

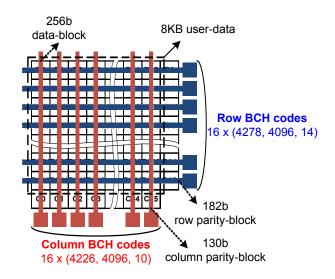

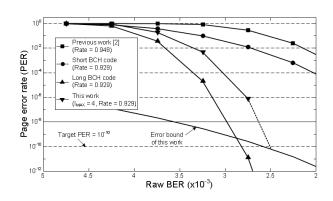

그림 1은 본 논문에서 사용된 (70528, 65536) CBCH 부호의 구조를 모사하고 있다. 8K-바이트 크기의 사용 자-데이터는 256-비트 단위의 데이터-블록(Bx)으로 나 누어지며, 데이터-블록은 16개의 row-방향 BCH 구성 부호와 16개의 column-방향 구성부호에 의하여 보호 된다. 보다 효과적인 오류정정을 위하여 row-방향은 (4278, 4096, 14) BCH 부호를, column-방향은 (4226, 4096, 10) BCH 부호를 사용한다. 이를 위하여 각 row 의 끝에는 row-방향 BCH 부호를 위한 16개의 182-비 트 패리티-블록(Rx)이 존재하며, 같은 이유로 16개의 130-비트 패리티-블록(Cx)이 각 column의 끝에 존재 한다. CBCH 부호는 row-방향과 column-방향의 복호 화 과정이 반복적으로 수행되면서 매우 강력한 오류정 정능력을 제공한다. 그림 2에서 표현되었듯 최대 4번 의 반복적 복호화 연산을 허용한 8K-바이트 CBCH 부호는 짧은 길이(512-바이트)의 구성부호만을 사요하 면서도 긴 길이(8K-바이트)의 BCH부호화 비슷한 오 류정정능력을 갖고 있다. 오류정정 복부호화 회로의 하드웨어 복잡도는 부호의 길이에 비례하여 증가하므 로, (70528, 65536) CBCH 부호는 낮은 복잡도의 하드 웨어만으로 강력한 성능을 제공함을 알 수 있다.

# 2.2 기존의 CBCH 부호화기

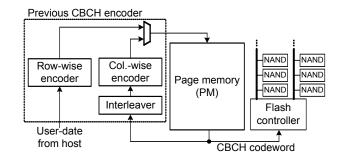

그림 3은 기존에 사용되던 CBCH 부호화기를 모사 하고 있다 [4-5]. 강력한 오류정정을 위하여 CBCH 부 호는 일반적으로 다른 row-방향, column-방향 구성부 호를 갖고 있으며 이를 지원하기 위한 row-방향, column-방향 부호화기가 필요하다. 고속의 호스트 인 터페이스로부터 전송된 8K-바이트 크기의 사용자-데 이터는 row-방향 부호기를 통과하면서 16개의 row-방 향 BCH 부호들을 생성한다. 이렇게 생성된 부호들은 페이지-메모리(PM)에 임시적으로 저장된다. Row-방 향의 부호화과정이 완료되면, 8K-바이트의 사용자-데 이터가 PM에서 다시 읽혀지며 인터리버를 거쳐서 column-방향으로 정렬된 데이터를 형성한다. 이어서 column-방향 부호화기를 이용한 column-방향 부호화 연산이 진행되면 16개의 column-방향 패리티-블록이 생성되어 PM에 저장된다. 위의 과정을 통하여 완성된 CBCH 부호는 그림 3에서 도시하였듯 플래시 컨트롤 러로 이동되어 실제 NAND 플래시에 프로그램 된다.

이러한 기존의 CBCH 부호화 과정은 한 번에 한쪽 방향의 부호화 연산을 수행하기에 1차원적인 부호화로 정의할 수 있으며, 이전 방향의 부호화가 종료된 뒤에

그림 1. (70528, 65536) CBCH 부호의 구조

그림 2. (70528, 65536) CBCH 부호의 성능

그림 3. 기존의 CBCH 부호화기의 구조

다른 방향의 부호화가 진행되기에 부호화에 많은 시간을 필요로 한다. 더욱이 기존의 1차원 부호화에서는 각 방향의 연산에서 독립적으로 사용자-데이터를 사용하여 불필요한 PM 접근을 야기한다. 즉 한 번의 CBCH 부호화 과정에 사용자-데이터를 두 번 접근하기에 높은 에너지효율을 갖는 단점이 존재한다.

#### 2013년도 대한전자공학회 하계학술대회 제36권 1호

## 2.3 제안된 2차원 부호화 기법

8K-바이트의 사용자-데이터를 한 번만 이용하여 CBCH 부호화를 진행하기 위하여 본 논문에선 2차원 부호화 기법을 제안한다. 이를 위하여 generatorpolynomial g(x)에 대한 부호화 과정을 표현하는 함수  $f_{g(x)}(x)$ 를 정의한다. 즉, 그림 1에서 k-번째 row에 해당 하는 512-바이트 사용자-데이터가  $D_{Rk}(x) = B16k(x) \times$  $\mathbf{x}^{256 \times 15}$  + B16k+1(x)×  $\mathbf{x}^{256 \times 14}$  +  $\cdots$  + B16k+15(x)로 정의 될 경우, k-번째 row-방향 BCH 부호는  $f_{g(x)}(D_{Rk}(x))$  =  $D_{Rk}(x) \times x^{\operatorname{order}(g(x))} + D_{Rk}(x) \mod g(x)$ 로 표현된다. 따라 서 row-방향의 부호화 과정은 해당 row-방향 부호화 기에  $D_{Rk}(x)$ 를 최상위-비트(MSB)부터 차례대로 인가 하여  $f_{\sigma(x)}(D_{Rk}(x))$ 를 구하는 동작으로 모델링 할 수 있 다. 이 때, 각  $D_{Rk}(x)$ 에 포함된 16개의 데이터-블록은 서로 다른 16개의 column-방향 부호를 만드는데 필요 한 부분적인 데이터-블록이다. 따라서 m-번째 column 인  $D_{Cm}(x)$ 중 k-번째 데이터-블록은 k-번째 row-방향 부호화과정에서 CBCH 부호화기에 존재한다.

제안하는 2차원 부호화 방식은 이렇게 존재하는  $D_{Cm}(x)$ 의 k-번째 데이터-블록만을 이용하여 부분적인 column-방향 부호화 연산을 row-방향 부호화 연산과 동시에 수행한다. 하나의 row-방향 연산이 16개의 서 로 다른 column-방향 데이터-블록을 사용하기에, 하나 의 row-방향 부호화에 16번의 부분적인 column-방향 부호화가 수행된다. 이를 지원하기 위하여 부분적으로 진행되는 16개의 column-방향 부호화의 내부 값을 임 시적으로 저장하기 위한 FIFO가 필요하다. 즉, row-방 향 부호화 중 하나의 256-비트 데이터-블록의 처리가 완료될 때 하나의 column-방향 부호에 대한 부분적 연산이 동시에 완료되며, 현재 column-방향 부호화기 에 있는 정보는 FIFO에 저장하고 다음 column-방향 부호의 정보를 FIFO에서 불러와서 이어지는 256-비트 데이터-블록에 대한 부호화를 진행한다. 따라서 제안 하는 방식은 16개의 row-방향 코드의 부호화를 수행 하면서 16개의 column-방향 부호화가 같이 진행되기 에 2차원 부호화로 정의 할 수 있으며, 1차원 부호화 에 비하여 부호화 시간을 절반으로 줄일 수 있다.

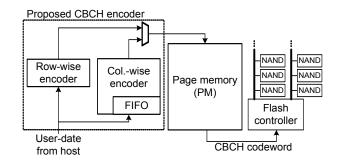

그림 4는 제안된 2차원 부호화 방식을 지원하는 CBCH 부호화기의 구조를 표현하고 있다. 기존의 부호화기에 사용되었던 인터리버 대신 column-방향 부호화기의 내부에 부분적 연산을 지원하기 위한 FIFO가 새롭게 도입되었다. 제안하는 구조에서는 8K-바이트에 해당하는 사용자-데이터가 호스트로부터 전송 될 경우 row-방향 부호화기와 column-방향 부호화기에 동시에 인가된다. Column-방향 부호화기는 내부의 FIFO를 이용하여 현재 인가되는 데이터-블록에 해당하는 부분적

그림 4. 제안하는 CBCH 부호화기의 구조

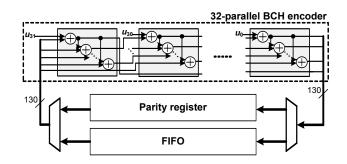

그림 5. 32-parallel column-방향 부호화기의 내부구조

인 부호화 연산을 수행한다. 따라서 제안하는 CBCH 부호화기 구조는 큰 하드웨어의 추가가 없이도 기존의 연산 부호화 속도를 2배 향상시킬 수 있다.

실제 구현 과정에서는 보다 고속의 부호화 속도를 얻기 위하여, 병렬화된 구조가 필요하다[6]. 제안하는 CBCH 부호화기는 각 방향의 부호화기에 32-비트의 사용자-데이터를 인가한다. 그림 5는 32-parallel 구조가 적용된 column-방향 부호화기의 내부 구조를 도시하고 있으며, 32-비트 단위로 인가되는 사용자-데이터 ( $u_x$ )와 130-비트에 해당하는 패리티-레지스터의 조합을 통하여 고속의 부호화가 가능함을 알 수 있다. 또한 내부적으로 존재하는 FIFO의 데이터가 추가적인지연시간 없이 바로 부호화기에 인가되는 구조를 채택하여 제안하는 2차원 부호화를 효과적으로 지원한다.

## Ⅲ. 구현

그림 4와 5에 모사된 2차원 부호화 방식을 적용한 8K-바이트 32-parallel CBCH 부호화기의 하드웨어 구조는 65nm CMOS 공정을 이용하여 구현되었으며, 그동작이 검증되었다. 구현된 부호화기는 250MHz로 동작하며, 78.3K개의 게이트를 필요로 한다. 제안된 2차원 부호화 방식으로 인하여 구현된 CBCH 부호화기는

### 2013년도 대한전자공학회 하계학술대회 제36권 1호

7.43Gb/s의 고속 부호화 속도를 지원한다. 기존의 구조들이 비슷한 속도를 내기 위하여 128-parallel 이상의 병렬화 계수를 사용하여 높은 복잡도를 야기하는 것을 고려하면[5], 제안하는 2차원 부호화기는 작은 병렬화계수만을 이용하면서도 높은 부호화 속도를 얻을 수 있으며 이를 통하여 전체 시스템의 복잡도를 획기적으로 줄일 수 있음을 알 수 있다.

## Ⅳ. 결론

본 논문에서는 MLC NAND 플래시 메모리를 이용하는 SSD 시스템의 신뢰도를 높이기 위한 CBCH 오류정정부호의 고속 부호화 기법을 기술하였다. 기존의 1차원 부호화 방식이 row-방향 및 column-방향의 부호화를 독립적으로 수행하는데 반해, 제안하는 2차원부호화 방식은 동시에 양 방향의 부호화를 진행하기에보다 작은 병렬화 계수만을 사용하여도 고속의 CBCH부호화기를 구현할 수 있다. 제안하는 2차원 부호화방식을 이용한 8KB CBCH 부호화기는 65nm CMOS공정이 이용하여 구현되었으며, 250MHz의 동작속도에서 7Gb/s 이상의 고속 부호화 속도를 실현하였다.

# Acknowledgement

This work was supported in part by IT R&D program of MKE/KEIT No.KI10035202 and by the IC Design Education Center (IDEC).

## 참고문헌

- [1] D. Lee *et al.*, "A 64Gb 533Mb/s DDR interface MLC NAND flash in sub-20nm technology," in Proc. *IEEE Int. Solid-State Circuits Conf.* (*ISSCC*), 2012, pp. 430-431.

- [2] Y. Lee *et al.*, "6.4Gb/s Multi-Threaded BCH Encoder and Decoder for Multi-Channel SSD Controllers," in Proc. *IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2012, pp. 426-427.

- [3] G. Dong, N. Xie and T. Zhang, "On the Use of Soft-Decision Error-Correction Codes in NAND Flash Memory," *IEEE Trans. Circuits Syst. I,* Reg. Papers, vol. 58, no. 2, pp. 429-439, Feb. 2011.

- [4] S. Cho and J. Ha, "Concatenated BCH Codes for NAND Flash Memories," in Proc. IEEE Int. Conf. Comm. (ICC), 2012, pp. 2639–2644.

- [5] K. Seki *et al.*, "Single-chip FEC codec using a concatenated BCH code for 10Gb/s long-haul optical transmission systems," in Proc. *IEEE Custom integr. Circuits Conf. (CICC)*, 2003, pp. 279–282.

- [6] S. Lin and D. J. Costello, Error control coding: Fundamentals and Applications, 2nd ed. Englewood Cliff, NJ: Prentice-Hall Inc., 2004.